Une approche au niveau du panneau (PL) de l’empaquetage de sortance (FO) a été discutée pendant plusieurs années pour réduire le coût de l’empaquetage FO à puce en premier basé sur la technologie de couche de redistribution (RDL). Plus récemment, des boîtiers multicouches haute densité à puce ont été introduits pour des applications plus avancées. Cette technologie bénéficierait également du traitement PL pour la réduction des coûts. En raison des grandes dimensions du boîtier, les applications telles qu’un processeur d’application (AP) ou un module multipuce (MCM) auront de plus grands avantages que les applications plus petites de circuit intégré de gestion de l’alimentation (PMIC), d’émetteur-récepteur ou de codec audio typiques du boîtier FO à puce en premier.

Les défis techniques connus avec l’empaquetage au niveau du panneau (PLFO) vont du décalage de matrice sur le panneau complet, en passant par le gauchissement du panneau le long du flux de processus, ce qui limite le nombre de couches de redistribution, jusqu’au contrôle de la variation d’épaisseur totale (TTV) pendant les processus de broyage arrière au niveau du panneau. Les aspects commerciaux tels que les dépenses en capital sur l’équipement au niveau du panneau et la difficulté à remplir une ligne de panneau sont les principales considérations financières.

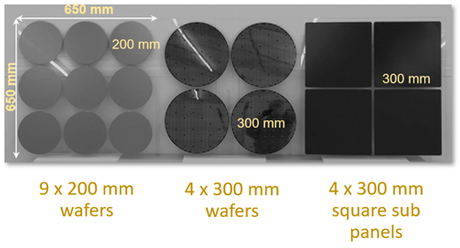

Une technologie PLFO de 650 mm x 650 mm sera présentée qui permet l’assemblage de quatre sous-panneaux de sortance ronds de 300 mm ou carrés de 300 mm sur un panneau porteur. Cette technologie permet la réutilisation de l’équipement de reconstitution et de traitement au niveau de la matrice / de l’emballage, en concentrant le traitement des panneaux là où le plus grand avantage en termes de coûts peut être obtenu dans le processus de couche de redistribution. L’utilisation d’un panneau de support minimise le gauchissement, permettant la mise en œuvre de plus de RDL sans affecter la capacité de traitement. La partie de reconstitution du flux est effectuée sur le plus petit facteur de forme, minimisant les considérations de décalage de matrice sur le grand panneau. Le même équipement et la même infrastructure de panneau peuvent également être utilisés pour les substrats PLFO à dernière puce ou les substrats sans noyau haute densité et de haute qualité. Les détails du flux de processus seront partagés sur la base d’une ligne pilote PLFO.

Les résultats de fiabilité au niveau des composants sur un véhicule de test de déploiement de la dernière puce seront présentés, ainsi qu’une modélisation comparative des coûts sur la première puce PLFO par rapport à la plaquette de déploiement de 300 mm pour les boîtiers de déploiement de la puce en premier et de la dernière puce.

Pour surmonter le souci de remplir une ligne de panneaux, une technologie de panneaux flexibles a été développée qui peut être utilisée dans une large gamme de technologies d’emballage.

Applications technologiques :

- Paquet d’échelle de puce au niveau de la tranche (WLCSP) – 300 mm, 200 mm, 150 mm [1]

- Wafer Level Fan-Out (WLFO) – Die en premier, couche de redistribution (RDL) en premier [2], [3]

- Système en package (SiP) [4]

Fig. 1 : Exemples de wafers et de panneaux assemblés sur un panneau de verre de 650 mm x 650 mm.

La technologie Hybrid Panel Level Package (Hybrid PLP) (HPLT) est basée sur un panneau grand format de 650 mm x 650 mm. Ce format de panneau permet de traiter quatre plaques ou panneaux carrés de 300 mm, neuf plaques de 200 mm ou 16 plaques de 150 mm.

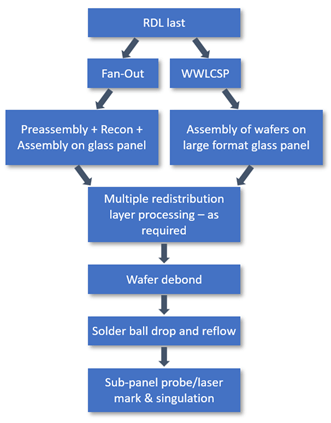

Le flux de processus après l’assemblage sur le panneau de verre est effectivement le même pour WLCSP, les premières tranches WLFO ou pour les panneaux de sortance au niveau du panneau (PLFO), comme illustré à la figure 1. Les descriptions des flux de processus WLCSP et WLFO sont illustrées à la figure 2.

Fig. 2 : Flux de processus pour WLCSP et diffusion en premier.

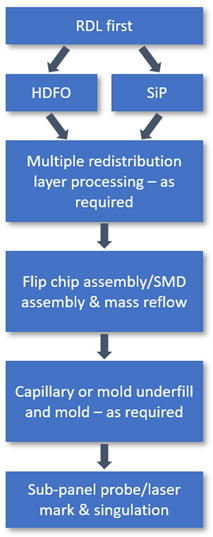

La plaquette ou le sous-panneau est assemblé sur un panneau de verre grand format à coefficient de dilatation thermique (CTE) adapté au moyen d’un adhésif de liaison temporaire. Les couches diélectriques sont appliquées dans un processus panneau par panneau approprié pour assurer une excellente uniformité de couche. L’exposition est effectuée sur un équipement pas à pas au niveau du panneau – l’alignement étant effectué sur une base individuelle de tranche ou de sous-panneau. Le processus de développement est à nouveau exécuté panneau par panneau. Le durcissement est effectué dans un four de durcissement à atmosphère contrôlée. La nomenclature (BOM) a été sélectionnée pour fournir des caractéristiques mécaniques et chimiques identiques des couches de redistribution traitées sur la ligne de traitement des tranches. Pour la dernière application de matrice ou la première application RDL de cette technologie, le flux de processus est inversé, comme le montre la figure 3.

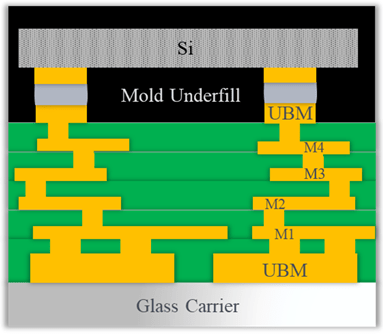

Les couches RDL sont construites directement sur le panneau de verre, en commençant par la couche de métallisation sous bosse (UBM) et en procédant de la couche RDL supérieure à la couche RDL inférieure avec les diélectriques intercouches respectifs. Après l’achèvement de la couche RDL inférieure, une couche UBM supplémentaire est nécessaire pour permettre l’assemblage flip-chip de la matrice sur la pile RDL. Après l’assemblage flip-chip, un processus de sous-remplissage de moule (MUF) ou, pour des applications à pas plus fin, un processus de sous-remplissage capillaire (CUF) et de moulage peut être utilisé pour compléter l’encapsulation du dispositif. Le panneau de verre peut ensuite être décollé du dispositif moulé. Les équipements de flip-chip et de moule actuellement disponibles nécessitent que le panneau de verre soit subdivisé en dimensions plus petites, ce qui signifie que le panneau de verre ne peut pas être réutilisé dans cette application. Cette limitation peut être surmontée en utilisant une puce retournée et un moulage au niveau du panneau.

Fig. 3 : Flux de processus pour les premières applications RDL.

Coût

HPLT se concentre sur les éléments les plus coûteux de toute technologie de redistribution – les couches de redistribution elles-mêmes. Les étapes de processus qui auront un avantage significatif en termes de coût d’un traitement massivement parallèle sont réalisées sur une base de panel. Cela comprend le revêtement et le développement des couches diélectriques et photorésistantes, l’exposition des couches diélectriques et des couches photorésistantes, le durcissement des couches diélectriques, le dépôt physique en phase vapeur des couches de germination, le dépôt électrochimique, la bande de photoréserve et la gravure humide chimique de la couche de germination restante.

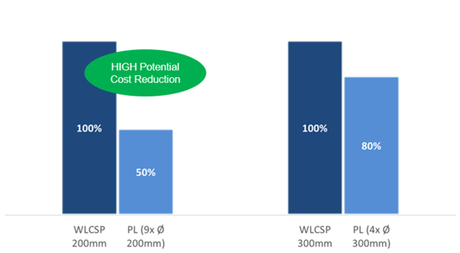

Cette stratégie offre des avantages significatifs en termes de coûts pour toutes les technologies d’emballage impliquées. Pour accéder correctement aux gains de coûts potentiels réalisables grâce à cette technologie, une modélisation des coûts a été réalisée pour les différentes applications. La comparaison la plus simple est possible avec les applications WLCSP, puisque toutes les considérations de dimension de matrice ou de boîtier peuvent être ignorées car seuls les coûts de traitement au niveau de la tranche sont pertinents pour la comparaison.

Fig. 4 : Comparaison des coûts pour les couches de redistribution réalisées sur les conceptions au niveau des tranches par rapport aux panneaux.

Ce que l’on peut observer à partir de la comparaison des coûts de la figure 4, c’est qu’un avantage de coût significatif peut être obtenu et que les avantages de coût s’améliorent avec des tranches plus petites à mesure que le rapport de la surface perdue à la surface utile diminue.

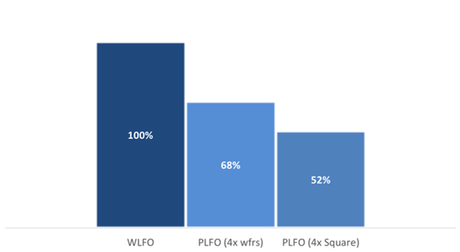

Pour l’application Fan Out, l’application matrice en premier est considérée car la matrice en dernier dépend trop des processus d’assemblage ultérieurs. Pour la première application de matrice, la comparaison est triple entre WLFO en tranche de 300 mm produite sur une ligne de traitement de tranches de 300 mm, 4 tranches rondes de 300 mm traitées et assemblées sur un panneau de 650 mm et enfin des panneaux carrés de 300 mm assemblés sur un panneau de 650 mm, comme illustré à la figure 5.

Fig. 5 : Comparaison des coûts pour les couches de redistribution effectuées sur les conceptions au niveau des tranches par rapport aux panneaux pour les applications en premier.

La simulation de coût effectuée a montré un avantage significatif du traitement de quatre tranches rondes de 300 mm assemblées sur le panneau grand format. Cependant, l’utilisation de la surface obtenue en utilisant quatre sous-panneaux carrés de 300 mm assemblés sur le panneau de verre conduit à des gains potentiels supplémentaires importants.

Description du véhicule d’essai

Pour démontrer les capacités de la technologie, un premier véhicule d’essai (TV) RDL à six couches métalliques a été sélectionné.

Fig. 6 : Structure du véhicule d’essai.

La structure multi-RDL a été construite sur un panneau de verre de 650 mm x 650 mm à l’aide de méthodes photolithographiques, comme décrit précédemment à la figure 3. Après l’achèvement du traitement RDL jusqu’à la métallisation sous bosse côté matrice (UBM), le panneau de verre a été sectionné en morceaux plus petits correspondant à la capacité de l’équipement d’assemblage ultérieur. Le placement des puces flip-chip a été effectué et les matrices ont été soudées par refusion de masse.

Le processus de moulage ultérieur a été appliqué pour encapsuler la matrice assemblée et également pour agir comme sous-remplissage de moule. Le décollement au laser a été utilisé pour dissocier le support RDL en verre de l’emballage encapsulé. Les emballages individuels ont été séparés à l’aide de dés à lame mécanique.

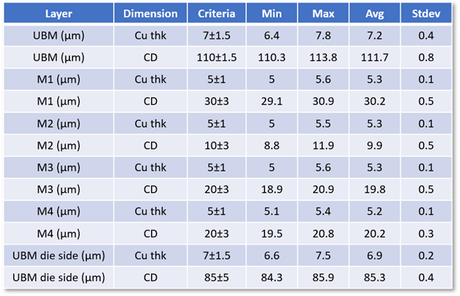

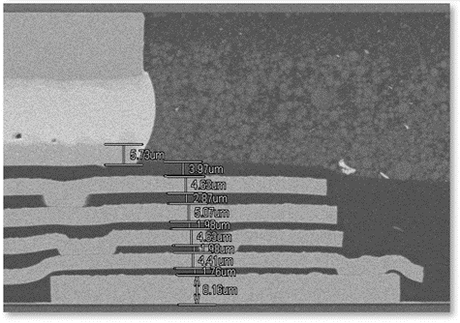

Les dimensions critiques minimales des couches de redistribution étaient un espace de ligne de 5 µm et une largeur de ligne de 5 µm. Les couches UBM avaient une épaisseur nominale de 7 µm, les 4 couches de redistribution avaient une épaisseur nominale de 5 µm et l’épaisseur des couches diélectriques était de 5 µm. Les données de mesure en ligne obtenues concernant les couches métalliques RDL sont présentées dans le tableau 1, avec toutes les valeurs bien dans la spécification définie.

Tableau 1 : Données relatives à la couche métallique.

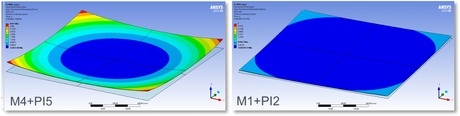

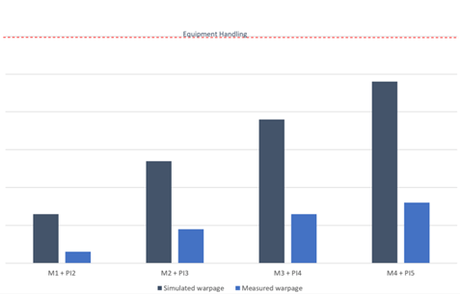

Un problème avec un panneau grand format avec plusieurs RDL est le gauchissement causé par le durcissement des différentes couches diélectriques et le décalage CTE entre le verre et le diélectrique. Avant de commencer les activités, une simulation par éléments finis a été effectuée pour évaluer le gauchissement attendu. L’empilement simulé était une structure à quatre couches RDL avec cinq couches diélectriques. Trois types de verre avec trois CTE différents allant d’un CTE bien adapté au silicium (Si), d’un CTE bien adapté à la première diffusion et d’une valeur CTE intermédiaire. Deux épaisseurs de panneaux ont été considérées en fonction du CTE.

Fig. 7 : Déformation du panneau après 1L RDL et 4L RDL.

Comme prévu, la simulation montre une accumulation d’effets de gauchissement avec des RDL supplémentaires (métal + diélectrique).

Fig. 8 : Gauchissement du panneau basé sur deux épaisseurs de panneau et trois CTE.

Le gauchissement simulé et le gauchissement mesuré concordent bien en tendance, cependant, l’ampleur du gauchissement observé était significativement inférieure à la simulation prédite et loin des spécifications de manipulation de l’équipement indiquées dans le graphique. Les discontinuités dans le film diélectrique étaient très probablement la cause de la différence.

Après l’achèvement des étapes d’assemblage suivantes, des coupes transversales mécaniques ont été réalisées pour analyser la structure des couches par rapport aux valeurs nominales et comme première évaluation de l’intégrité de l’emballage.

Fig. 9 : Épaisseur de couche mesurée en coupe à 0 heures.

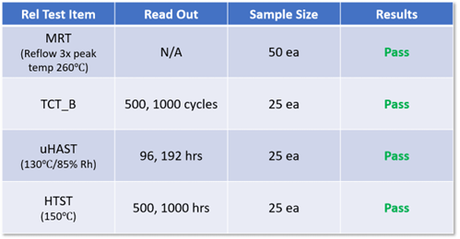

Les unités isolées ont été soumises à une série de tests de fiabilité. L’objectif principal de cette évaluation de la fiabilité était l’adhérence des couches et l’intégrité de l’emballage. Les résultats des tests de fiabilité effectués sont présentés dans le tableau 2. Tous les résultats étaient positifs et aucun échec n’a été observé après les tests de résistance.

Tableau 2 : Résultats de fiabilité au niveau des composants.

Conclusion

Cet article a présenté une nouvelle plate-forme technologique d’emballage au niveau du panneau. La flexibilité de la plate-forme pour une utilisation dans les conceptions WLCSP, WLFO et PLFO, à la fois dans les configurations die-first et die-last, a été démontrée. Les résultats d’un véhicule de test multicouche die-last ont été présentés, affichant une excellente fiabilité avec une nomenclature identique à celle du boîtier équivalent au niveau de la plaquette. Les résultats de la modélisation des coûts ont démontré les gains significatifs réalisables avec cette technologie.

Les problèmes de déformation pour les structures RDL multicouches soulevés par la simulation n’ont pas été confirmés avec les données en ligne – les données montrant une marge de manipulation significative. L’évaluation de la fiabilité a prouvé l’intégrité de l’emballage des derniers emballages traités en utilisant le format de panneau de 650 mm x 650 mm.

Sur la base des résultats à ce jour, d’autres études sont encouragées pour explorer pleinement la fabricabilité et la fiabilité de cette technologie d’emballage.

Remerciements

Les auteurs tiennent à souligner la contribution de Nathan Whitchurch à la réalisation de la simulation de déformation et remercient l’équipe de développement au niveau de la plaquette ATK5 pour son soutien dans cette étude.

Les références

[1] P. Garou et al., “Wafer level chip scale packaging (WL-CSP): an overview,” IEEE Transactions on Advanced Packaging (Volume:23, issue 2, May 2000, PP. 198 – 205, DOI: 10.1109/6040.846634.

[2] M. Brunnbauer, E. Fürgut, G. Beer, T. Meyer, « Embedded Wafer Level Ball Grid Array (eWLB) », 2006 8th Electronics Packaging Technology Conference. 6-8 déc. 2006, DOI : 10.1109/EPTC.2006.342681.

[3] Norikazu Motohashi, Takehiro Kimura, Kazuyuki Mineo, Yusuke Yamada, Tomohiro Nishiyama, Koujiro Shibuya, Hiroaki Kobayashi, Yoichiro Kurita, Masaya Kawano, «System in Wafer-Level Package Technology with rdl-First Process». ) Doi: 10.1109 / ectc.2011.5898492.

[4] T. Wakabayashi, « La technologie FOWLP en tant que système au niveau de la plaquette dans la solution d’emballage (SiP) », Conférence internationale 2017 sur l’emballage électronique (ICEP), 19-22 avril 2017, DOI : 10.23919/ICEP.2017.7939429.

Abonnez-vous à notre page Facebook: https://www.facebook.com/mycamer.net

Pour recevoir l’actualité sur vos téléphones à partir de l’application Telegram cliquez ici: https://t.me/+KMdLTc0qS6ZkMGI0

Nous ecrire par Whatsapp : Whatsapp +44 7476844931